- +91 636 634 3323

- hr@moorecorevlsi.com

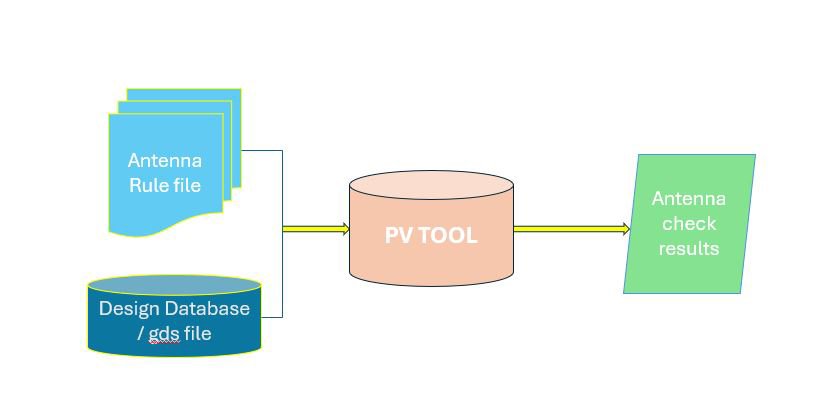

Physical Verification in the context of VLSI (Very Large Scale Integration) refers to the process of checking whether the physical layout of an integrated circuit adheres to design rules and constraints. This step is crucial to ensure the manufacturability and reliability of the semiconductor device. The physical verification process involves analyzing the layout of the circuit design with respect to various geometric and electrical constraints.

Physical verification tools are employed in this process, and they play a crucial role in identifying and rectifying potential issues before the semiconductor fabrication process begins. The goal is to ensure that the final manufactured chip meets the design specifications and functions reliably.